HP Pavilion 17t ab series Quanta G37A G37B r1A (PDF)

File information

Title: G37A_N16E-GR-M4G_3D_1228-2130

Author: 96100127

This PDF 1.3 document has been generated by PDFCreator 2.2.2.0 / Mac OS X 10.12.6 Quartz PDFContext, and has been sent on pdf-archive.com on 06/04/2018 at 18:24, from IP address 89.66.x.x.

The current document download page has been viewed 1899 times.

File size: 2.78 MB (51 pages).

Privacy: public file

File preview

1

2

3

4

5

6

7

8

POWER PAVILION PARFAIT INTEL SKL / KABY -H SYSTEM DIAGRAM 01

For Layout Review

Charge

Config#3 SODIMM 1DPC

PG.40

A

DDR4

SODIMM1

DDR4 2133MHz

STD

Channel A

Max. 8GB

PG.42

PG.17

CPU Core

PG.43~45

SODIMM2

Max. 8GB

+1.0V/+1.2VSUS

RSV

PG.47~48

PG.18

DDR4 2133MHz

Channel B

PEG

X8 Lane

INTEL

NVIDIA N16P-GX / N16E-GR

VRAM gDDR5 x 4pcs

Package 29 x 29mm

256M x16 / 256M x32

2.5GHz

PG.14~25

40W

Sky Lake - H4+2

Kaby Lake - H4+2

DP portE

Processor : Quad Core

Power : 45 (Watt)

Package : BGA1440

Size : 42 x 28 (mm)

Die Size : 13.6 x 9.1 (mm)

PG.19~23

27MHz

PAGE 21

PS8409 re-driver IC

HDMI v2.0

PG.27

PG.27

eDP (5.4Gb/s) eDP

17" eDP Panel

HD/FHD/UHD

PG.2~8

+3V/+5V S5

PG.26

DMI

PG.41

STACKUP

TOP

GND

IN1

IN2

VCC

IN3

GND

BOT

A

SATA 6GB/s

B

+VGACORE

M.2 2280-S3 SSD

PG.49

PG.33

+1.35V_GFX

PG.50

HDD

SATA1B

PG.32

SATA 6GB/s

USB 3.0 Ports

INTEL PCH

SATA 1.5GB/s

Lynx Point

Power : Watt

Package : FCBGA837

Size : 23 x 23 (mm)

LANE5

PG.31

3D CAM

Intel SR300 3D

PG.31

PG.30

PORT2

PORT3

PORT4

PG.30

LANE7

USB3.0 Re-Driving IC

PTN36241G

USB 3.0 Ports

(DB)

PORT1

USB 2.0 Ports

(DB)

PCI-E x 1 Gen1

C

PORT4

USB 2.0

SATA3

PG.32

PORT2

PG.30

SATA2

PG.32

ODD

B

PORT1

LANE9,10,11,12

SATA 6GB/s

HDD

USB 3.0

SATA0A

PCIEx4 4GB/s

PORT5

HD+ IR CAM

(OPTION)

HD CAM

PG.26

PG.26 +PG.34

LANE6

C

USB 2.0

LAN

RTL8111HSH/ Gbe

Card Reader

RTS5237S-GR

PG.35

WLAN

BT COMBO

PG.36

PORT7

I2C

Touch Screen

I2C0

PG.33

Synaptics S7817

PG.26

G-Sensor

HP2DC

ROM

PG.34

D

PG.34

TP

PG.38

Azalia

LPC

KBC

ITE IT8987E/BX

KB

PG.9~16

PG.12

SMBUS

TPM 2.0 SLB9665TT2.0

(OPTION)

SPI

LPC

AUDIO CODEC

PG.37

ALC3258-CG

FAN

PG.38

Headphone amplifier

HPA0022642RTJR

PG.29

PG.28

PG.38

Speaker

PG.28

Dual Digital MIC

PG.28

Hp

MIC

Combo Jack

(DB)

D

PG.30

PROJECT : G37A/G37B

Quanta Computer Inc.

3D CAM MIC

/ INT CAM MIC

Size

Custom

PG.26

Document Number

Date: Monday, December 28, 2015

1

2

3

4

5

6

7

Rev

1A

01 -- Block Diagram

Sheet

8

1

of

51

5

4

3

+1.0V

5,6,10,16,37,48

+VCCSTPLL

6,43,47

Host CLK:

Trace length < 11000 mils

Trace spacing = 15 / 20 mils, Impendence 85 ohm

U1E

Ra

D

PCH_PECI

37

EC_PECI

R2

13/F_4

EC_PECI

Ca

C2

*47P/50V_4

11

11

CLK_CPU_BCLKP

CLK_CPU_BCLKN

11

11

CPU_PCI_BCLKP

CPU_PCI_BCLKN

11

11

R4

H_PROCHOT#

Cb

H_PROCHOT#_R

499/F_4

CLK_DPLL_NSCCLKP

CLK_DPLL_NSCCLKN

18

DDR_VTT_CNTL

C3

*47P/50V_4

11

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

11

11

PM_SYNC

H_PM_DOWN

13

SKTOCC_N_R

CPU_PLTRST#R

12,16,19,33,34,35,36,37

R11

PLTRST#

B31

A32

CPU_PCI_BCLKP

CPU_PCI_BCLKN

D35

C36

H_CPU_SVIDALRT#

VR_SVID_CLK_R

H_CPU_SVIDDAT

H_PROCHOT#_R

BH31

BH32

BH29

BR30

DDR_VTT_CNTL

BT13

H_VCCST_PWRGD

PM_SYNC (50ohm)

Trace Length: 1~11.25 inches

C

CLK_CPU_BCLKP

CLK_CPU_BCLKN

CLK_DPLL_NSCCLKP E31

CLK_DPLL_NSCCLKN D31

PROCHOT# (50ohm)

Trace Length <11 inches

Cb need placment near VR

37,43

1

02

SKYLAKE Processor (CLK,MISC,JTAG)

H_PECI (50ohm)

Trace Length: <0.5 iches

Ra,Ca need placement close to PCH.

11

2

CPU_PLTRST#R

*1.5K/F_4

20_4

SKTOCC_N_R R15

0_4

SKTOCC_N

PROC_SEL#

BR33

BN1

BM30

*10K_4 CATERR#

R16

+VCCSTPLL

R13

*750/F_4

H_PM_DOWN_R

EC_PECI

PM_THRMTRIP#

BT31

BP35

BM34

BP31

BT34

J31

PROCPWRGD

CPU_PLTRST#R

R19

H13

Processor pull-up (CPU)

SKYLAKE_HALO

BGA1440

BCLKP

BCLKN

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

CFG[17]

CFG[16]

CFG[19]

CFG[18]

VCCST_PW RGD

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROCPW RGD

RESET#

PM_SYNC

PM_DOW N

PECI

THERMTRIP#

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

SKTOCC#

PROC_SELECT#

CATERR#

CFG_RCOMP

5 OF 14

*SKL_H_BGA_BGA

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

BN23

BP23

BP22

BN22

CFG16

CFG17

CFG18

CFG19

BR27

BT27

BM31

BT30

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

BT28

BL32

BP28

BR28

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TMS_CPU

XDP_TRST#_CPU

BP30

BL30

BP27

XDP_TRST#

XDP_PREQ#

XDP_PRDY#

BT25

CFG_RCOMP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

16

16

8,16

8,16

8,16

8,16

8,16

16

16

16

8,16

16

8,16

8,16

16

16

CFG16

CFG17

CFG18

CFG19

16

16

16

16

XDP_BPM0

XDP_BPM1

TP2

TP1

XDP_TRST#

XDP_PREQ#

XDP_PRDY#

49.9/F_4

+1.0V

51_4

*51_4

*51_4

*51_4

+1.0V

XDP_TRST#_CPU R10

XDP_TRST#

R12

C

Design Note(CFG_RCOMP):

DEFENSIVE DESIGN 50-OHM FOR R40PR (SV REQ)

HWPD

Ra close to CPU side

H_VCCST_PWRGD trace 0.3" - 1.5"

PROCPWRGD

PROCPWRGD

R9

*10K_4

Close to CPU

+VCCSTPLL

R21

1K_4

R26

*54.9/F_4

R22

*1K_4

SVID CLK

VR_SVID_CLK_R

R27

0_4

VR_SVID_CLK

51_4

51_4

15,16

15,16

15,16

+1.0V

B

D

16

16

+VCCSTPLL

PLACE THE PU RESISTORS

CLOSE TO VR

PULL UP IS IN THE VR MODULE

1K_4

R5

R6

R7

R8

R17

PROCPWRGD (50ohm)

Trace Length: 1~11.25 inches

10

R3

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TDI_CPU

XDP_PREQ#

XDP_TDO_CPU

16

XDP_TDI_CPU

16

XDP_TMS_CPU

16

XDP_TRST#_CPU

16

CPU CORE SVID

Layout note:

1.Need routing together

2.ALERT need between CLK and DATA.

H_PROCHOT#

B

Ra

43

10,16,37,41,42,47,48

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

Rb need placment near PCH

HWPG

D2 1

2 RB500V-40

H_VCCST_PWRGD_R

60.4/F_4 H_VCCST_PWRGD

R24

C4

*10P/50V_4

+VCCSTPLL

Close to CPU

CLOSE TO CPU

PLACE THE PU RESISTORS

H_CPU_SVIDALRT#

R25

R23

56.2/F_4

5,11,37

SVID ALERT

220/F_4

PM_THRMTRIP#

+VCCSTPLL

VR_SVID_ALERT#

PM_THRMTRIP#

Rb

R14

CPU VDDQ

1K_4

Note: please keep plane is enough for VDDQ 2.8A

43

C5

*0.1U/10V_4

Ra(R10804) Not install in SKL-H

+1.2VSUS

+VCCSTPLL

A

CLOSE TO CPU

PLACE THE PU RESISTORS

+VCCSTPLL

0.1U/16V_4

C7

*0.1U/10V_4

A

R18

*10K_4

Close to CPU

PROC_SEL#

SVID DATA

R29

C6

Ra

R28

100/F_4

H_CPU_SVIDDAT

Placement close to CPU.

0_4

VR_SVID_DATA

PROJECT : G37A/G37B

Quanta Computer Inc.

R20

*0_4

43

Size

Custom

Document Number

Date: Monday, December 28, 2015

5

4

3

2

Rev

1A

02 -- SKL 1/7 (JTAG/MISC)

1

Sheet

2 of

51

5

+VCCIO

4

6,16,48

3

2

1

03

SKYLAKE Processor (DMI,PEG,FDI)

U1C

SKYLAKE_HALO

BGA1440

19

19

PEG_RXP0

PEG_RXN0

E25

D25

19

19

PEG_RXP1

PEG_RXN1

E24

F24

19

19

PEG_RXP2

PEG_RXN2

19

19

PEG_RXP3

PEG_RXN3

19

19

PEG_RXP4

PEG_RXN4

E21

D21

19

19

PEG_RXP5

PEG_RXN5

E20

F20

19

19

PEG_RXP6

PEG_RXN6

E19

D19

19

19

PEG_RXP7

PEG_RXN7

E23

D23

D

dGPU

E22

F22

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

PEG_RCOMP

Trace length < 400 MILS

Trace width = 12 MILS

Trace spacing = 15 MILS

C

+VCCIO

DMI

9

9

DMI_RXP0

DMI_RXN0

9

9

DMI_RXP1

DMI_RXN1

9

9

DMI_RXP2

DMI_RXN2

9

9

DMI_RXP3

DMI_RXN3

R30

D11

E11

F10

E10

24.9/F_4 PEG_COMPG2

D8

E8

E6

F6

D5

E5

J8

J9

PEG_RXP[0]

PEG_RXN[0]

PEG_TXP[0]

PEG_TXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_TXP[1]

PEG_TXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_TXP[2]

PEG_TXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_TXP[3]

PEG_TXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_TXP[4]

PEG_TXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_TXP[5]

PEG_TXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_TXP[6]

PEG_TXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_TXP[7]

PEG_TXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_TXP[8]

PEG_TXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_TXP[9]

PEG_TXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_TXP[10]

PEG_TXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_TXP[11]

PEG_TXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_TXP[12]

PEG_TXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_TXP[13]

PEG_TXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_TXP[14]

PEG_TXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_TXP[15]

PEG_TXN[15]

B25 PEG_TXP0_C

A25 PEG_TXN0_C

C8

C9

0.22U/10V_4

0.22U/10V_4

B24 PEG_TXP1_C

C24 PEG_TXN1_C

C10

C11

0.22U/10V_4

0.22U/10V_4

B23 PEG_TXP2_C

A23 PEG_TXN2_C

C12

C13

0.22U/10V_4

0.22U/10V_4

B22 PEG_TXP3_C

C22 PEG_TXN3_C

C14

C15

0.22U/10V_4

0.22U/10V_4

B21 PEG_TXP4_C

A21 PEG_TXN4_C

C16

C17

0.22U/10V_4

0.22U/10V_4

B20 PEG_TXP5_C

C20 PEG_TXN5_C

C18

C19

0.22U/10V_4

0.22U/10V_4

B19 PEG_TXP6_C

A19 PEG_TXN6_C

C20

C21

0.22U/10V_4

0.22U/10V_4

B18 PEG_TXP7_C

C18 PEG_TXN7_C

C22

C23

0.22U/10V_4

0.22U/10V_4

PEG_TXP0

PEG_TXN0

19

19

PEG_TXP1

PEG_TXN1

19

19

PEG_TXP2

PEG_TXN2

19

19

PEG_TXP3

PEG_TXN3

19

19

PEG_TXP4

PEG_TXN4

19

19

PEG_TXP5

PEG_TXN5

19

19

PEG_TXP6

PEG_TXN6

19

19

PEG_TXP7

PEG_TXN7

19

19

BOM:

DIS : Stuff

UMA: Un-Stuff

D

dGPU

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C

C10

B10

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_TXP[0]

DMI_TXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_TXP[1]

DMI_TXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_TXP[2]

DMI_TXN[2]

DMI_RXP[3]

DMI_RXN[3]

DMI_TXP[3]

DMI_TXN[3]

B8

A8

C6

B6

B5

A5

D4

B4

DMI_TXP0

DMI_TXN0

9

9

DMI_TXP1

DMI_TXN1

9

9

DMI_TXP2

DMI_TXN2

9

9

DMI_TXP3

DMI_TXN3

9

9

DMI

3 OF 14

*SKL_H_BGA_BGA

U1D

B

K36

K37

J35

J34

H37

H36

J37

J38

D27

E27

11/05 change HDMI from APU to GPU

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

A

SKYLAKE_HALO

BGA1440

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

DDI1_AUXP

DDI1_AUXN

EDP_AUXP

EDP_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

EDP_DISP_UTIL

EDP_RCOMP

D29

E29

F28

E28

B29

A29

B28

C28

INT_EDP_TXP0

INT_EDP_TXN0

INT_EDP_TXP1

INT_EDP_TXN1

INT_EDP_TXN2

INT_EDP_TXP2

INT_EDP_TXN3

INT_EDP_TXP3

C26

B26

INT_eDP_AUXP

INT_eDP_AUXN

A33

EDP_DISP_UTIL

D37

EDP_RCOMP

26

26

26

26

26

26

26

26

INT_eDP_AUXP

INT_eDP_AUXN

26

26

eDP

TP3

R31

24.9/F_4

+VCCIO

DP & PEG Compensation

y

DDI2_AUXP

DDI2_AUXN

eDP_RCOMP

Trace length < 100 Mils

Trace Width 20 Mils Trace Spacing 25 Mils

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

B

INT_EDP_TXP0

INT_EDP_TXN0

INT_EDP_TXP1

INT_EDP_TXN1

INT_EDP_TXN2

INT_EDP_TXP2

INT_EDP_TXN3

INT_EDP_TXP3

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

G27

G25

G29

AUD_AZACPU_SCLK

AUD_AZACPU_SDO_R

AUD_AZACPU_SDI_R R32

20_4

AUD_AZACPU_SCLK

10

AUD_AZACPU_SDO_R

10

AUD_AZACPU_SDI

10

A

4 OF 14

*SKL_H_BGA_BGA

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

4

3

2

Rev

1A

03 -- SKL 2/7 (DMI/EDP/PEG)

Date: Monday, December 28, 2015

5

1

Sheet

3

of

51

5

4

3

2

1

04

SKYLAKE Processor (DDR4)

18

U1A

17

BGA1440

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

BGA1440

M_A_DQ[63:0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

D

C

B

BR6

BT6

BP3

BR3

BN5

BP6

BP2

BN3

BL4

BL5

BL2

BM1

BK4

BK5

BK1

BK2

BG4

BG5

BF4

BF5

BG2

BG1

BF1

BF2

BD2

BD1

BC4

BC5

BD5

BD4

BC1

BC2

AB1

AB2

AA4

AA5

AB5

AB4

AA2

AA1

V5

V2

U1

U2

V1

V4

U5

U4

R2

P5

R4

P4

R5

P2

R1

P1

M4

M1

L4

L2

M5

M2

L5

L1

BA2

BA1

AY4

AY5

BA5

BA4

AY1

AY2

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKP[1]

DDR0_CKN[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_W E#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[3]

DDR0_MA[4]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ECC[0]

DDR0_ECC[1]

DDR0_ECC[2]

DDR0_ECC[3]

DDR0_ECC[4]

DDR0_ECC[5]

DDR0_ECC[6]

DDR0_ECC[7]

DDR0_DQSP[8]

DDR0_DQSN[8]

AG1

AG2

AK2

AK1

AL3

AK3

AL2

AL1

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

17

17

M_A_CS#0

M_A_CS#1

17

17

M_A_DIM0_ODT0

M_A_DIM0_ODT1

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

17

17

17

17

M_A_CKE0

M_A_CKE1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

AG3

AU5

17

17

17

M_A_RAS#

M_A_WE#

M_A_CAS#

M_A_A[13:0]

17

17

17

17

M_A_BG#1

M_A_ACT#

17

17

M_A_PARITY

M_A_ALERT#

17

17

BR5

BL3

BG3

BD3

AA3

U3

P3

L3

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSN[7:0]

17

BP5

BK3

BF3

BC3

AB3

V3

R3

M3

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSP[7:0]

17

BT11

BR11

BT8

BR8

BP11

BN11

BP8

BN8

BL12

BL11

BL8

BJ8

BJ11

BJ10

BL7

BJ7

BG11

BG10

BG8

BF8

BF11

BF10

BG7

BF7

BB11

BC11

BB8

BC8

BC10

BB10

BC7

BB7

AA11

AA10

AC11

AC10

AA7

AA8

AC8

AC7

W8

W7

V10

V11

W 11

W 10

V7

V8

R11

P11

P7

R8

R10

P10

R7

P8

L11

M11

L7

M8

L10

M10

M7

L8

AW 11

AY11

AY8

AW 8

AY10

AW 10

AY7

AW 7

AY3

BA3

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKP[1]

DDR1_CKN[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_W E#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[3]

DDR1_MA[4]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_ECC[0]

DDR1_ECC[1]

DDR1_ECC[2]

DDR1_ECC[3]

DDR1_ECC[4]

DDR1_ECC[5]

DDR1_ECC[6]

DDR1_ECC[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

AM9

AN9

AM7

AM8

AM11

AM10

AJ10

AJ11

M_B_CLKP0

M_B_CLKN0

M_B_CLKP1

M_B_CLKN1

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

18

18

18

18

M_B_CKE0

M_B_CKE1

18

18

M_B_CS#0

M_B_CS#1

18

18

D

M_B_DIM0_ODT0

M_B_DIM0_ODT1

AH10

AH11

AF8

AH8

AH9

AR9

AJ9 M_B_A0

AK6 M_B_A1

AK5 M_B_A2

AL5 M_B_A3

AL6 M_B_A4

AM6 M_B_A5

AN7 M_B_A6

AN10 M_B_A7

AN8 M_B_A8

AR11 M_B_A9

AH7 M_B_A10

AN11 M_B_A11

AR10 M_B_A12

AF9 M_B_A13

AR7

AT9

18

18

M_B_RAS#

M_B_WE#

M_B_CAS#

18

18

18

M_B_BS#0

M_B_BS#1

M_B_BG#0

M_B_A[13:0]

18

18

18

18

C

M_B_BG#1

M_B_ACT#

AJ7

AR8

18

18

M_B_PARITY

M_B_ALERT#

18

18

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSN[7:0]

18

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_DQSP[7:0]

18

B

AW 9

AY9

DDR CHANNEL B

R33

R34

R35

DDR CHANNEL A

17

17

M_A_BS#0

M_A_BS#1

M_A_BG#0

SKYLAKE_HALO

U1B

M_B_DQ[63:0]

SKYLAKE_HALO

121/F_4

75/F_4

100/F_4

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

G1

H1

J2

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

BN13 +SM_VREF

BP13

BR13 SMDDR_VREF_DQ1_M3

SM_VREF

17

TP8503

SMDDR_VREF_DQ1_M3

18

2 OF 14

*SKL_H_BGA_BGA

1 OF 14

*SKL_H_BGA_BGA

A

A

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

Date: Monday, December 28, 2015

5

4

3

2

Rev

1A

04 -- SKL 3/7 (DDR4 I/F)

1

Sheet

4

of

51

5

4

+3VPCU

10,30,33,37,38,40,41

+3V

9,10,11,12,13,14,16,17,18,19,22,26,27,28,29,30,32,33,34,35,36,37,38,43,46,49

+1.0V

2,6,10,16,37,48

+VCCGT

7,43,45

3

2

1

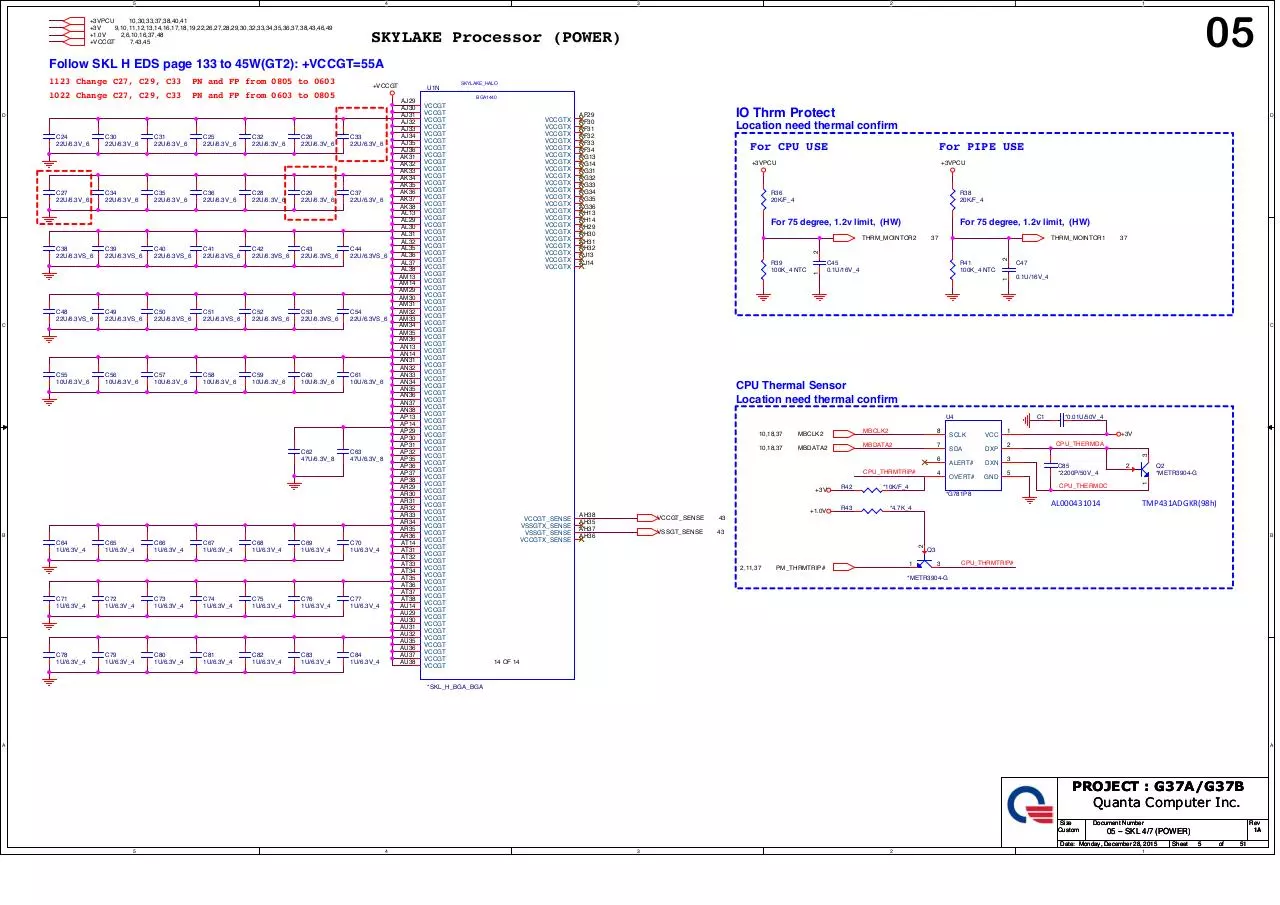

05

SKYLAKE Processor (POWER)

Follow SKL H EDS page 133 to 45W(GT2): +VCCGT=55A

C48

22U/6.3VS_6

C39

22U/6.3VS_6

C49

22U/6.3VS_6

C35

22U/6.3V_6

C40

22U/6.3VS_6

C50

22U/6.3VS_6

C25

22U/6.3V_6

C36

22U/6.3V_6

C41

22U/6.3VS_6

C51

22U/6.3VS_6

C32

22U/6.3V_6

C28

22U/6.3V_6

C42

22U/6.3VS_6

C52

22U/6.3VS_6

C26

22U/6.3V_6

C29

22U/6.3V_6

C43

22U/6.3VS_6

C53

22U/6.3VS_6

C33

22U/6.3V_6

C37

22U/6.3V_6

C44

22U/6.3VS_6

C54

22U/6.3VS_6

C

C55

10U/6.3V_6

C56

10U/6.3V_6

C57

10U/6.3V_6

C58

10U/6.3V_6

C59

10U/6.3V_6

C60

10U/6.3V_6

C62

47U/6.3V_8

C61

10U/6.3V_6

C63

47U/6.3V_8

B

C64

1U/6.3V_4

C65

1U/6.3V_4

C66

1U/6.3V_4

C67

1U/6.3V_4

C68

1U/6.3V_4

C69

1U/6.3V_4

C70

1U/6.3V_4

C71

1U/6.3V_4

C72

1U/6.3V_4

C73

1U/6.3V_4

C74

1U/6.3V_4

C75

1U/6.3V_4

C76

1U/6.3V_4

C77

1U/6.3V_4

C78

1U/6.3V_4

C79

1U/6.3V_4

C80

1U/6.3V_4

C81

1U/6.3V_4

C82

1U/6.3V_4

C83

1U/6.3V_4

C84

1U/6.3V_4

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

IO Thrm Protect

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

D

Location need thermal confirm

For CPU USE

For PIPE USE

+3VPCU

+3VPCU

R36

20K/F_4

R38

20K/F_4

For 75 degree, 1.2v limit, (HW)

For 75 degree, 1.2v limit, (HW)

THRM_MOINTOR2

37

THRM_MOINTOR1

37

R39

100K_4 NTC

C45

0.1U/16V_4

R41

100K_4 NTC

C47

0.1U/16V_4

C

CPU Thermal Sensor

Location need thermal confirm

U4

10,18,37

MBCLK2

MBCLK2

8

10,18,37

MBDATA2

MBDATA2

7

6

CPU_THRMTRIP#

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

AH38

AH35

AH37

AH36

VCCGT_SENSE

43

VSSGT_SENSE

43

+3V

R42

+1.0V

R43

4

C1

SCLK

VCC

SDA

DXP

ALERT#

DXN

OVERT#

GND

*0.01U/50V_4

1

2

+3V

CPU_THERMDA

3

C38

22U/6.3VS_6

C34

22U/6.3V_6

C31

22U/6.3V_6

3

5

2

C85

*2200P/50V_4

CPU_THERMDC

*10K/F_4

Q2

*METR3904-G

1

C27

22U/6.3V_6

C30

22U/6.3V_6

BGA1440

2

C24

22U/6.3V_6

SKYLAKE_HALO

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

1

D

U1N

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

*G781P8

AL000431014

*4.7K_4

TMP431ADGKR(98h)

B

2

+VCCGT

2

PN and FP from 0805 to 0603

PN and FP from 0603 to 0805

1

1123 Change C27, C29, C33

1022 Change C27, C29, C33

2,11,37

1

PM_THRMTRIP#

Q3

3

CPU_THRMTRIP#

*METR3904-G

14 OF 14

*SKL_H_BGA_BGA

A

A

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

Date: Monday, December 28, 2015

5

4

3

2

Rev

1A

05 -- SKL 4/7 (POWER)

1

Sheet

5

of

51

5

4

3

2

1

06

+1.2VSUS

2,10,17,18,42,46,48,51

+VCCIO

3,16,48

+VCCSTPLL

2,43,47

+VCCSA

43,45

Follow SKL H EDS page 135 45W: VDDQ=2.8A

Follow SKL H EDS page 135 to 45W(GT2): VCCSA=11.1A

+VCCSA

+1.2VSUS

SKYLAKE_HALO

U1I

D

C106

10U/6.3V_6

C93

10U/6.3V_6

C86

10U/6.3V_6

C94

22U/6.3VS_6

C87

22U/6.3VS_6

C90

10U/6.3V_6

C91

10U/6.3V_6

C92

10U/6.3V_6

C107

10U/6.3V_6

C100

1U/6.3V_4

C101

1U/6.3V_4

C110

1U/6.3V_4

+VCCIO

Follow SKL H EDS P136 to 45W: VCCIO

+VCCIO = 0.95V

C112

22U/6.3VS_6

C113

22U/6.3VS_6

C

C114

1U/6.3V_4

C115

1U/6.3V_4

C116

10U/6.3V_6

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

U1J

BGA1440

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

11.1 A

2.8 A

5.5 A

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCPLL_OC

0.26 A VCCPLL_OC

C95

22U/6.3VS_6

C88

22U/6.3VS_6

C96

22U/6.3VS_6

C89

22U/6.3VS_6

C108

10U/6.3V_6

C109

10U/6.3V_6

C97

10U/6.3V_6

C98

10U/6.3V_6

C99

10U/6.3V_6

C102

10U/6.3V_6

C103

10U/6.3V_6

C104

10U/6.3V_6

C105

10U/6.3V_6

C111

10U/6.3V_6

Y12

+VDDQC

BH13

G11

+VCCPLL_OC +VCCSTPLL

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

D

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

C

0.12 A

VCCST

VCCSTG

VCCSTG

0.145 A

VCCPLL

VCCPLL

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

H30

BL15

BM16

H29

C117

1U/6.3V_4

+VCCSTG

BL22

BM22

G30

H28

J28

+VCCPLL

M38

M37

H14

J14

VCCSA_SENSE

VSSSA_SENSE

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

+VCCIO

43

43

BP15

BR15

BT15

R46

100_4

BP16

BR16

BT16

VCCIO_VCCSENSE

VSSIO_VSSSENSE

BN15

BM15

R49

100_4

BP17

BN16

9 OF 14

BM14

BL14

*SKL_H_BGA_BGA

Under CPU

SKYLAKE_HALO

BGA1440

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

BJ35

BJ36

Close CPU

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

B

B

+VDDQC

+VCCSTG

+VCCPLL_OC

+VCCIO

+VCCPLL

+VDDQC

+1.2VSUS

R44

C118

C119

C120

C121

C122

C123

10U/6.3V_6

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

TP76

TP77

0_6

+VCCPLL_OC

+1.2VSUS

R45

AT13

AW13

R53

R54

R55

*0_6

*49.9/F_4

*49.9/F_4

*49.9/F_4

TP6

TP7

CPU_OPC_COMP

CPU_OPCE_COMP

CPU_OPCE_COMP2

AU13

AY13

BT29

BR25

BP25

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

+1.2V_VCCPLL_OC

R47

+VCCIO

C124

C125

*1U/6.3V_4

*22U/6.3V_6

10 OF 14

*SKL_H_BGA_BGA

0_6

+VCCPLL

Unconnected for Processors without OPC.

+VCCSTPLL

R48

0_6

R50

0_4

R51

*0_4

R52

*0_4

+VCCSTG

+VCCSTPLL

+1.0V

A

A

+VCCIO

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

4

3

2

Rev

1A

06 -- SKL 5/7 (POWER&GND )

Date: Monday, December 28, 2015

5

1

Sheet

6

of

51

5

4

3

2

1

07

+VCC_CORE

44

+VCCGT

5,43,45

+VCC_CORE

+VCC_CORE

U1G

D

Follow SKL H EDS page 131 to 45W(GT2): VCC_CORE=68A

C

B

C205

47U/6.3V_8

C206

47U/6.3V_8

VCC_SENSE

VSS_SENSE

AG37

AG38

2

2

2

2

2

2

C158

0.1U/16V_4

C175

0.1U/16V_4

C176

0.1U/16V_4

Sense resistor should be placed within 2

inches (50.8 mm) of the processor socket

Trace Impendence 50 ohm

+VCC_CORE

R56

100/F_4

VCC_SENSE

VSS_SENSE

1

C204

1U/6.3V_4

2

C203

1U/6.3V_4

C200

1U/6.3V_4

1

C202

1U/6.3V_4

C199

1U/6.3V_4

C174

0.1U/16V_4

C138

0.1U/16V_4

2

C201

1U/6.3V_4

C198

1U/6.3V_4

C157

0.1U/16V_4

1

C196

10U/6.3V_6

1

C195

10U/6.3V_6

2

C194

10U/6.3V_6

1

C193

10U/6.3V_6

C173

0.1U/16V_4

C137

0.1U/16V_4

2

C192

10U/6.3V_6

C156

0.1U/16V_4

1

C191

10U/6.3V_6

1

C190

10U/6.3V_6

2

C189

10U/6.3V_6

1

C188

10U/6.3V_6

C172

0.1U/16V_4

C148

0.1U/16V_4

2

C187

10U/6.3V_6

C155

0.1U/16V_4

1

C186

10U/6.3V_6

1

C185

10U/6.3V_6

2

C184

22U/6.3V_6

1

C183

22U/6.3V_6

C171

0.1U/16V_4

C136

0.1U/16V_4

2

C182

22U/6.3V_6

C154

0.1U/16V_4

1

C181

22U/6.3V_6

1

C180

22U/6.3V_6

2

C179

22U/6.3V_6

C170

0.1U/16V_4

C153

0.1U/16V_4

1

C178

22U/6.3V_6

C169

0.1U/16V_4

C147

0.1U/16V_4

2

C177

22U/6.3V_6

C168

0.1U/16V_4

C146

0.1U/16V_4

1

C167

22U/6.3V_6

2

C166

22U/6.3V_6

1

C165

22U/6.3V_6

2

C164

22U/6.3V_6

1

C163

22U/6.3V_6

2

C162

22U/6.3V_6

C152

0.1U/16V_4

1

C161

22U/6.3V_6

C151

0.1U/16V_4

2

C160

22U/6.3V_6

C150

0.1U/16V_4

1

C144

22U/6.3V_6

2

C143

22U/6.3V_6

1

C142

22U/6.3V_6

C135

0.1U/16V_4

2

C149

22U/6.3V_6

C134

0.1U/16V_4

1

C141

22U/6.3V_6

1

C159

22U/6.3V_6

C133

0.1U/16V_4

2

C140

22U/6.3V_6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

1

C139

22U/6.3V_6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

2

C145

22U/6.3V_6

1

C132

22U/6.3V_6

1

C131

22U/6.3V_6

2

C130

22U/6.3V_6

1

C129

22U/6.3V_6

2

C128

22U/6.3V_6

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

1

C127

22U/6.3V_6

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

2

BGA1440

C126

22U/6.3V_6

C197

1U/6.3V_4

+VCCGT

SKYLAKE_HALO

VCC_SENSE

VSS_SENSE

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

U1H

+VCCGT

SKYLAKE_HALO

D

BGA1440

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

C

8 OF 14

*SKL_H_BGA_BGA

B

43

43

R57

100/F_4

7 OF 14

*SKL_H_BGA_BGA

VCC_SENSE

R58

VSS_SENSE

*49.9/F_4

A

A

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

4

3

2

Rev

1A

07 -- SKL 6/7 (POWER&GND )

Date: Monday, December 28, 2015

5

1

Sheet

7

of

51

5

4

3

2

1

08

SKL-HProcessor (GND)

U1F

D

C

B

Y38

Y37

Y14

Y13

Y11

Y10

Y9

Y8

Y7

W 34

W 33

W 12

W5

W4

W3

W2

W1

V30

V29

V12

V6

U38

U37

U6

T34

T33

T14

T13

T12

T11

T10

T9

T8

T7

T5

T4

T3

T2

T1

R30

R29

R12

P38

P37

P12

P6

N34

N33

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

M14

M13

M12

M6

L34

L33

L30

L29

K38

K11

K10

K9

K8

K7

K5

K4

K3

K2

U1L

SKYLAKE_HALO

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

6 OF 14

*SKL_H_BGA_BGA

K1

J36

J33

J32

J25

J22

J18

J10

J7

J4

H35

H32

H25

H22

H18

H12

H11

G28

G26

G24

G23

G22

G20

G18

G16

G14

G12

G10

G9

G8

G6

G5

G4

F36

F31

F29

F27

F25

F23

F21

F19

F17

F15

F13

F11

F9

F8

F5

F4

F3

F2

E38

E35

E34

E9

E4

D33

D30

D28

D26

D24

D22

D20

D18

D16

D14

D12

D10

D9

D6

D3

C37

C31

C29

C27

D38

C17

C13

C9

BT32

BT26

BT24

BT21

BT18

BT14

BT12

BT9

BT5

BR36

BR34

BR29

BR26

BR24

BR21

BR18

BR14

BR12

BR7

BP34

BP33

BP29

BP26

BP24

BP21

BP18

BP14

BP12

BP7

BN34

BN31

BN30

BN29

BN24

BN21

BN20

BN19

BN18

BN14

BN12

BN9

BN7

BN4

BN2

BM38

BM35

BM28

BM27

BM26

BM23

BM21

BM13

BM12

BM9

BM6

BM2

BL29

BK29

BK15

BK14

BJ32

BJ31

BJ25

BJ22

BH14

BH12

BH9

BH8

BH5

BH4

BH1

BG38

BG13

BG12

BF33

BF12

BE29

BE6

BD9

BC34

BC12

BB12

U1M

SKYLAKE_HALO

SKYLAKE_HALO

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

C25

C23

C21

C19

C15

C11

C8

C5

BM29

BM25

BM18

BM11

BM8

BM7

BM5

BM3

BL38

BL35

BL13

BL6

BK25

BK22

BK13

BK6

BJ30

BJ29

BJ15

BJ12

BH11

BH10

BH7

BH6

BH3

BH2

BG37

BG14

BG6

BF34

BF6

BE30

BE5

BE4

BE3

BE2

BE1

BD38

BD37

BD12

BD11

BD10

BD8

BD7

BD6

BC33

BC14

BC13

BC6

BB30

BB29

BB6

BB5

C2

BT36

BT35

BT4

BT3

BR38

BB4

BB3

BB2

BB1

BA38

BA37

BA12

BA11

BA10

BA9

BA8

BA7

BA6

B9

AY34

AY33

AY14

AY12

AW 30

AW 29

AW 12

AW 5

AW 4

AW 3

AW 2

AW 1

AV38

AV37

AU34

AU33

AU12

AU11

AU10

AU9

AU8

AU7

AU6

AT30

AT29

AT6

AR38

AR37

AR14

AR13

AR5

AR4

AR3

AR2

AR1

AP34

AP33

AP12

AP11

AP10

AP9

AP8

AN30

AN29

AN12

AN6

AN5

AM38

AM37

AM12

AM5

AM4

AM3

AM2

AM1

AL34

AL33

AL14

AL12

AL10

AL9

AL8

AL7

AL4

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

13 OF 14

*SKL_H_BGA_BGA

12 OF 14

*SKL_H_BGA_BGA

AK30

AK29

AK4

AJ38

AJ37

AJ6

AJ5

AJ4

AJ3

AJ2

AJ1

AH34

AH33

AH12

AH6

AG30

AG29

AG11

AG10

AG8

AG7

AG6

AF14

AF13

AF12

AF4

AF3

AF2

AF1

AE34

AE33

AE6

AD30

AD29

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AC38

AC37

AC12

AC6

AC5

AC4

AC3

AC2

AC1

AB34

AB33

AB6

AA30

AA29

AA12

A30

A28

A26

A24

A22

A20

A18

A16

A14

A12

A10

A9

A6

B37

B3

A34

A4

A3

SKL-H Processor (RESERVED, CFG)

SKYLAKE_HALO

U1K

BGA1440

D1

E1

E3

E2

TP8

TP12

TP14

TP9

BR1

BT2

TP17

TP10

BN35

J24

H24

BN33

BL34

N29

R14

AE29

AA14

A36

A37

15

PCH_2_CPU_TRIG

CPU_2_PCH_TRIG_R

H23

J23

F30

E30

B30

C30

G3

J3

BR35

BR31

BH30

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

VSS

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PROC_TRIGIN

PROC_TRIGOUT

VSS

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

BM33

BL33

TP11

TP13

BJ14

BJ13

D

TP15

TP16

BK28

BJ28

BJ18

BJ16

BK16

TP18

TP19

BK24

BJ24

TP20

TP21

BK21

BJ21

BT17

BR17

BK18

BJ34

BJ33

TP22

TP23

C

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

11 OF 14

*SKL_H_BGA_BGA

CPU_2_PCH_TRIG_R

R59

30_4

CPU_2_PCH_TRIG

CPU_2_PCH_TRIG

15

Processor Strapping

The CFG signals have a default value of '1' if not terminated on the board.

B

0 Enable; SET DFX ENABLED BIT IN DEBUG

1 , Disable;

2,16

CFG3

CFG3

R60

*1K_4

2,16

CFG2

CFG2

R61

*1K_4

2,16

CFG4

CFG4

R62

1K_4

2,16

CFG5

CFG5

R63

*1K_4

2,16

CFG6

CFG6

R64

*1K_4

2,16

CFG10

CFG10

R65

*1K_4

2,16

CFG12

CFG12

R66

*1K_4

2,16

CFG13

CFG13

R67

*1K_4

A

A

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

Date: Monday, December 28, 2015

5

4

3

2

Rev

1A

08 -- SKL 7/7 (GND)

1

Sheet

8

of

51

5

4

3

+3V_DEEP_SUS

10,12,13,14,16,18

+3V

5,10,11,12,13,14,16,17,18,19,22,26,27,28,29,30,32,33,34,35,36,37,38,43,46,49

2

1

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

D

DMI_TXN0

DMI_TXP0

DMI_RXN0

DMI_RXP0

DMI_TXN1

DMI_TXP1

DMI_RXN1

DMI_RXP1

DMI_TXN2

DMI_TXP2

DMI_RXN2

DMI_RXP2

DMI_TXN3

DMI_TXP3

DMI_RXN3

DMI_RXP3

R73

Cardreader

WLAN

LAN

PCIE_RXN5_CARD

PCIE_RXP5_CARD

PCIE_TXN5_CARD

PCIE_TXP5_CARD

PCIE_RXN6_WLAN

PCIE_RXP6_WLAN

PCIE_TXN6_WLAN

PCIE_TXP6_WLAN

PCIE_RXN7_LAN

PCIE_RXP7_LAN

PCIE_TXN7_LAN

PCIE_TXP7_LAN

C207

C208

100/F_4

0.1U/16V_4

0.1U/16V_4

C209

C210

0.1U/16V_4

0.1U/16V_4

C211

C212

0.1U/16V_4

0.1U/16V_4

PCIECOMP_N

PCIECOMP_P

B18

C17

H15

G15

A16

B16

B19

TP24

C19

E17

TP25

G17

L17

K17

B20

C20

E20

TP26

G19

B21

A21

K19

TP27

L19

PCIE_TXN5_CARD_C D22

PCIE_TXP5_CARD_C C22

G22

E22

PCIE_TXN6_WLAN_C B22

PCIE_TXP6_WLAN_C A23

L22

K22

PCIE_TXN7_LAN_C C23

PCIE_TXP7_LAN_C B23

K24

L24

C24

B24

TP28

+3V

DMI_RXN0

DMI_RXP0

DMI_TXN0

DMI_TXP0

DMI_RXN1

DMI_RXP1

DMI_TXN1

DMI_TXP1

DMI_RXN2

DMI_RXP2

DMI_TXN2

DMI_TXP2

DMI_RXN3

DMI_RXP3

DMI_TXN3

DMI_TXP3

DMI

USB 2.0

PCIE_RCOMPN

PCIE_RCOMPP

PCIE1_RXN/USB3_7_RXN

PCIE1_RXP/USB3_7_RXP

PCIE1_TXN/USB3_7_TXN

PCIE1_TXP/USB3_7_TXP

PCIE2_TXN/USB3_8_TXN

PCIE2_TXP/USB3_8_TXP

PCIE2_RXN/USB3_8_RXN

PCIE2_RXP/USB3_8_RXP

PCIE3_RXN/USB3_9_RXN

PCIE3_RXP/USB3_9_RXP

PCIE3_TXN/USB3_9_TXN

PCIE3_TXP/USB3_9_TXP

PCIE4_RXN/USB3_10_RXN

PCIE4_RXP/USB3_10_RXP

PCIE4_TXN/USB3_10_TXN

PCIE4_TXP/USB3_10_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

PCIE6_TXP

PCIE7_RXN

PCIE7_RXP

PCIE7_TXN

PCIE7_TXP

PCIE8_RXN

PCIE8_RXP

PCIE8_TXN

PCIE8_TXP

PCIe/USB 3

C

36

36

36

36

33

33

33

33

35

35

35

35

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2N_11

USB2P_11

USB2N_12

USB2P_12

USB2N_13

USB2P_13

USB2N_14

USB2P_14

AF5

AG7

AD5

AD7

AG8

AG10

AE1

AE2

AC2

AC3

AF2

AF3

AB3

AB2

AL8

AL7

AA1

AA2

AJ8

AJ7

W2

W3

AD3

AD2

V2

V1

AJ11

AJ13

USBP1USBP1+

USBP2USBP2+

USBP3USBP3+

USBP4USBP4+

USBP5USBP5+

30

30

30

30

30

30

26

26

34

34

USBP7USBP7+

USB2.0 Combo USB3.0 MB-1

USB2.0 Combo USB3.0 Small Board

USB2.0 USB2.0 Small Board

USB30_TX1USB30_TX1+

USB30_RX1USB30_RX1+

30

30

USB30_TX2USB30_TX2+

USB30_RX2USB30_RX2+

USB3.0 (Small Board) 30

30

C11

B11

B7

A7

B12

A12

C8

B8

USB2_COMP

USB2_VBUSSENSE

RSVD_AB13

USB2_ID

GPD7/RSVD

TP29

B14

C14

G13

H13

TP30

D13

C13

A9

B10

TP8515

B13

A14

G11

E11

USB30_TX4+

USB30_TX4USB30_RX4+

USB30_RX4-

A

GPP_A5/LFRAME#/ESPI_CS0#

GPP_A6/SERIRQ/ESPI_CS1#

GPP_A7/PIRQA#/ESPI_ALERT0#

GPP_A0/RCIN#/ESPI_ALERT1#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

USB3_5_TXN

USB3_5_TXP

USB3_5_RXN

USB3_5_RXP

GPP_G19/SMI#

GPP_G18/NMI#

USB3_3_TXP/SSIC_2_TXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_RXN/SSIC_2_RXN

USB3_4_TXP

USB3_4_TXN

USB3_4_RXP

USB3_4_RXN

SPT_PCH_H

SATA

USB3.0 (3D Camera)

31

31

31

31

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_6_TXN

USB3_6_TXP

USB3_6_RXN

USB3_6_RXP

R74

R75

R76

R77

10K_4

10K_4

10K_4

10K_4

33

33

WLAN

GPP_E6/DEVSLP2

GPP_E5/DEVSLP1

GPP_E4/DEVSLP0

GPP_F9/DEVSLP7

GPP_F8/DEVSLP6

GPP_F7/DEVSLP5

GPP_F6/DEVSLP4

GPP_F5/DEVSLP3

6 OF 12

D

GFX Present

Rb

Ra

*100K_4 GPU_EVENT#

R78

BOM:UMA only

R79

+3V

10K_4

BOM:DIS only

DIS only

AD43 DGPU_HOLD_RST#

AD42 GPU_EVENT#

AD39 DGPU_PWR_EN

AC44 DGPU_PWROK

Y43 USB_OC4#

Y41 USB_OC5#

W 44 USB_OC6#

W 43 PCH_AOCS#

DGPU_HOLD_RST#

12,19

GPU_EVENT#

12,22

DGPU_PWR_EN

12,51

DGPU_PWROK

12,23,37,50

UMA

Stuff

Ra

Rb

NC

Rb

Ra

C

AG3 USB2_COMP R80

AD10

AB13

AG2

BD14

R405

*1K_4

113/F_4

R406

*1K_4

If OTG is not implemented on the platform,

then USB2_ID and USB2_VBUSSENSE should both

be connected to ground.

USB 2.0 PORT

USB

B15

C15

K15

K13

USB_OC4#

USB_OC5#

USB_OC6#

PCH_AOCS#

+3V_DEEP_SUS

SPT-H_PCH

USB3_1_TXN

USB3_1_TXP

USB3_1_RXN

USB3_1_RXP

*10K_4

10K_4

10K_4

10K_4

10K_4

SG(Default)

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_F15/USB2_OCB_4

GPP_F16/USB2_OCB_5

GPP_F17/USB2_OCB_6

GPP_F18/USB2_OCB_7

LPC/eSPI

USB3.0 (M/B-1)

30

30

30

30

R68

R69

R70

R71

R72

IR CAM

2 OF 12

U2F

DGPU_HOLD_RST#

DGPU_PWR_EN

DGPU_PWROK

SIO_EXT_SMI#

EC_RCIN#

HD / IR CAM

SPT_PCH_H

B

09

SPT-H_PCH

U2B

L27

N27

C27

B27

E24

G24

B28

A28

G27

E26

B29

C29

L29

K29

B30

A30

AT22

AV22

AT19

BD16

BE16

BA17

AW 17

AT17

BC18

BC17

AV19

LAD0

LAD1

LAD2

LAD3

SERIRQ

SERIRQ

BOARD_ID8

BOARD_ID7

LFRAME#

33,34,37

BOARD_ID8

EC_RCIN#

BOARD_ID7

SIO_EXT_SMI#

GC6_FB_EN

DEVSLP0

GC6_FB_EN

DEVSLP0

R81

8.2K_4

R82

R83

22/F_4

22/F_4

R84

EC2

*22/F_4

13

37

13

EC1

CLK_PCI_EC_R

CLK_PCI_LPC_R

M45

N43

AE45

AG43

AG42

AB39

AB36

AB43

AB42

AB41

33,34,37

33,34,37

33,34,37

33,34,37

33

USB2 MB

PORT1

USB3 MB

PORT2

USB2 DB

PORT2

USB3 DB

PORT3

USB2 DB

PORT3

NC

PORT4

PORT4

3D CAMERA

PORT5

HD /IR CAM

(OPTION)

IR CAM (OPTION)

PORT6

NC

PORT7

WLAN

PORT8

NC

PORT9-14

NC

B

34,37

+3V

18P/50V_4

CLK_24M_KBC

37

CLK_24M_DEBUG

33

37

22

USB 3.0 PORT

PORT1

18P/50V_4

EMI(near PCH)

CLK_PCI_TPM

34

Ra

For SSD (SATA0A)

Place to PCH

BOM: HW TPM need Ra, Rc Stuff

A

PROJECT : G37A/G37B

Quanta Computer Inc.

Size

Custom

Document Number

Date: Monday, December 28, 2015

5

4

3

2

Rev

1A

09 -- PCH 1/7 (DMI/USB/PCIE)

1

Sheet

9

of

51

Download HP Pavilion 17t-ab series Quanta G37A G37B r1A

HP Pavilion 17t-ab series Quanta G37A_G37B r1A.pdf (PDF, 2.78 MB)

Download PDF

Share this file on social networks

Link to this page

Permanent link

Use the permanent link to the download page to share your document on Facebook, Twitter, LinkedIn, or directly with a contact by e-Mail, Messenger, Whatsapp, Line..

Short link

Use the short link to share your document on Twitter or by text message (SMS)

HTML Code

Copy the following HTML code to share your document on a Website or Blog

QR Code to this page

This file has been shared publicly by a user of PDF Archive.

Document ID: 0000754047.